1. Introduction

In computing, the ALU is a fundamental combinational logic circuit designed to execute a wide range of arithmetic and logic operations. As a core component of the CPU, the ALU performs essential operations for data processing, including addition, subtraction, multiplication, division, and logic functions such as AND, OR, and XOR.As the demand for computational efficiency continues to grow, optimizing the performance and capabilities of the ALU has become crucial for meeting the needs of modern digital systems [1].

This paper focuses on exploring the design and optimization strategies for ALUs. It delves into various application scenarios, such as low-power computing in embedded systems, quantum computing, and high-speed processing in supercomputers. By analyzing recent innovations, including GDI technology, reversible logic, and Quantum Cellular Automata (QCA), the purpose of this paper is to discuss the possible optimization space of the current ALU to adapt to the needs of many different fields. Ultimately, this research contributes to the ongoing efforts to refine ALU designs, offering a pathway to more efficient and adaptable processors that can meet the evolving demands of diverse applications.

2. Theoretical Analysis of ALU

2.1. Definition and Basic Principles of ALU

The ALU plays an important role in the computing architecture [2]. Even the most basic microprocessors incorporate an ALU to handle core computational tasks. The ALU typically interfaces with the processor’s control unit, memory, and I/O devices through the bus protocol. With the advancement of Field-Programmable Gate Array (FPGA) technology, the design of customized ALUs tailored to specific application requirements have become a practical solution.

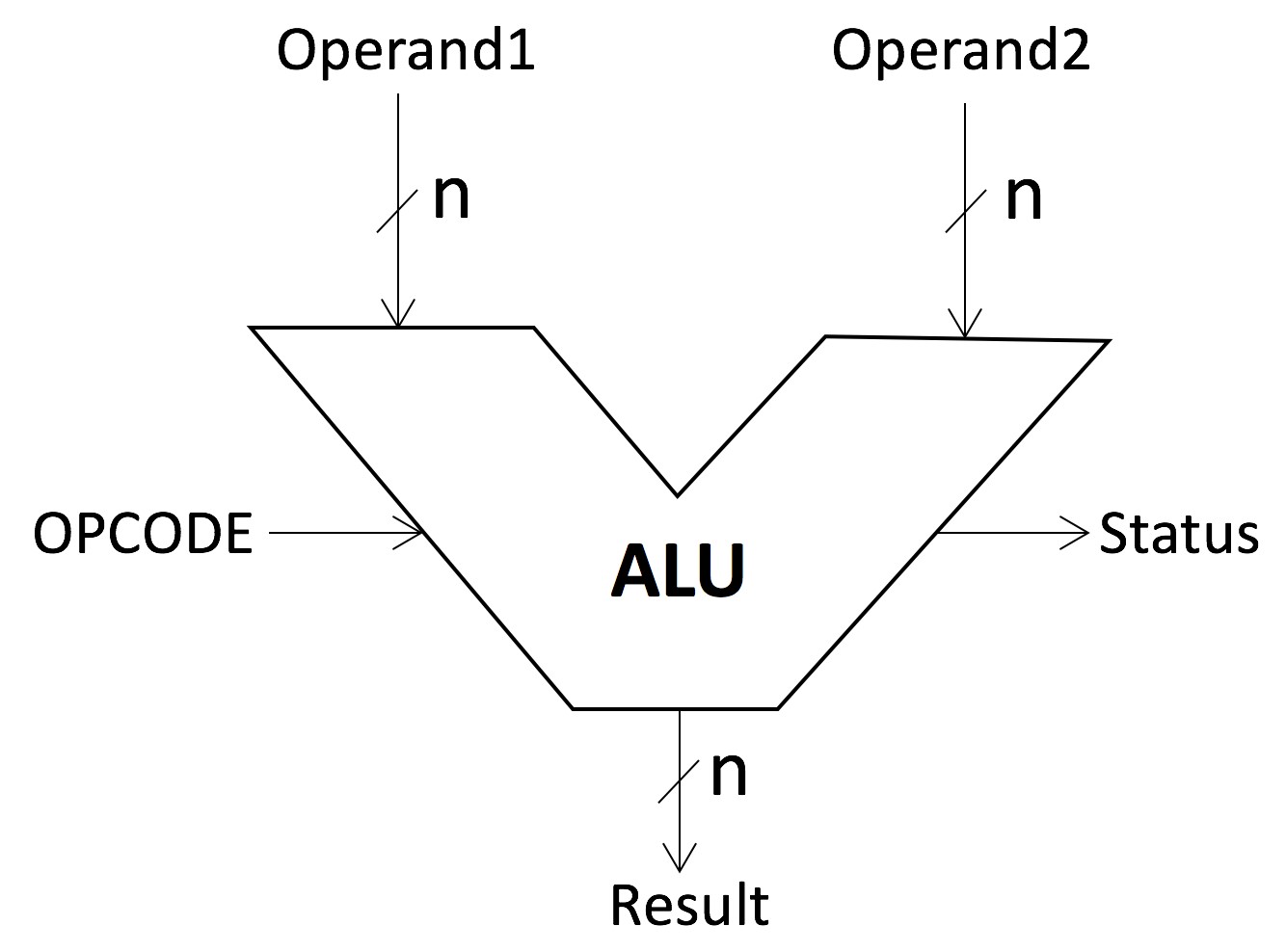

The Arithmetic Logic Unit (ALU) is responsible for performing arithmetic and logical operations on the data provided by the system. The ALU is designed as a combinational logic circuit, which means it produces outputs directly based on the inputs without involving any storage elements or clock signals. This makes the ALU extremely efficient for real-time computation. The structure of ALU is shown in Figure 1 [3].

Figure 1: ALU structure [3]

The ALU typically functions in conjunction with the processor’s control unit, which provides the necessary instructions and directs the ALU on which operations to perform on the input data. These data inputs are often fetched from the registers or memory, and the results of the operations are either stored back into registers or passed to other components of the system. Given the versatility of the ALU, it can handle integer operations, binary shifting, and comparison tasks. This makes it indispensable in tasks ranging from simple calculations to complex decision-making processes. For example, in the realm of digital signal processing (DSP), filtering, signal transformation, and data compression are all depends on the ALU’s ability to process data.

2.2. Functions of ALU Modules

The ALU is composed of several sub-modules, each designed to handle specific types of operations:

Adder/Subtractor Module: This module performs binary addition and subtraction. The implementation leverages an adder circuit where the input operands are processed based on the control signal K. For example, it can use 4 full adders connected in series. Each adder processes a single bit from the two 4-bit inputs. For addition (K=0), the two binary numbers are added directly. The circuit uses XOR gates to manage the subtraction operation. For subtraction (K=1), the two’s complement of the subtrahend is computed by inverting the bits and adding 1, effectively converting the subtraction into an addition problem

Logic Module handles bitwise logical operations such as AND, OR, XOR, and NOT. In Verilog, logical operations are used to perform Boolean algebra operations on variables. These operations are fundamental in designing digital circuits and performing logical decision-making processes within the CPU or DSP unit.

Shifter Module allows for bit-shifting operations, including logical shifts (left and right) and arithmetic shifts. Shifting is crucial in tasks such as multiplying or dividing integers by powers of two and manipulating binary data efficiently in various algorithmic implementations.

Multiplier Module was designed for the multiplication operation in the proposed ALU. The Array Multiplier shifts and add all at once. The Array Multiplier is also called a parallel multiplier. It needs a ‘array’ of adders. The Array Multiplier has three components – full adders, half adders and AND gates. Multiplication is often one of the more resource-intensive operations in an ALU, particularly in DSP applications where real-time processing of signals is required.

Comparator Module compares two binary numbers and generates a result indicating their relationship (equal, greater than, or less than). This function is widely used in decision-making processes, such as conditional branching in software or filtering in signal processing.

In modern digital systems, ALUs are often optimized for specific applications, with certain modules being enhanced or omitted depending on the computational needs of the system. In high-performance processors, multiple ALUs may operate in parallel to increase throughput [4].

3. ALU application scenarios and optimization strategies

As a core part of the processor, the performance of the ALU significantly impacts the overall computational efficiency and energy consumption of the system. It is very important to optimize the design of alu for embedded systems, image processing, quantum computing, high performance computing and other application scenarios. This paper explores different application contexts for ALUs, highlighting their use in low-power devices, quantum computing, and high-efficiency processors. It also summarizes various optimization strategies, such as Gate Diffusion Input (GDI) technology, Dual Mode Logic (DML), reversible logic, and Single Electron Transistor (SET), aimed at improving key performance metrics like power consumption, delay, and circuit area. These studies provide valuable insights into future ALU designs, helps to find the right solution in different computing environments

3.1. Low-Power and Approximate Computing in Image Processing Applications

In power-sensitive embedded systems and image processing applications, traditional precise computations are often not optimal, particularly when computational accuracy has a limited impact on the final result. Recent research by Mohammad Mirzaei has shown that approximate arithmetic units can provide an effective solution in such scenarios. By employing approximate adders, it is possible to significantly reduce power consumption, delay, and chip area, while allowing a tolerable level of error. Such a design is especially suitable for image processing tasks in embedded devices. Research findings indicate that using this method can decrease the power-delay product (PDP) without significantly affecting output quality, making it an effective solution for meeting the energy efficiency requirements of embedded systems [5].

3.2. High-Speed Computing with Superconducting Logic

In high-performance computing scenarios, ALU speed and efficiency are critical for the overall performance of the processor. To address this need, one study by Guang-Ming Tang has proposed an ALU design based on Rapid Single-Flux Quantum (RSFQ) technology. This design uses a parallel-prefix Ladner-Fischer adder, combined with a 16-bit bit-slice structure, to increase data processing throughput. By employing multi-stage pipelines and synchronous concurrent clocking, the design exhibits excellent performance in terms of computational speed and energy efficiency. The research findings indicate that RSFQ-based ALUs achieve higher frequencies and lower power consumption in superconducting environments, making them highly suitable for high-frequency, high-throughput computing tasks [6].

3.3. High-Performance Coprocessors in Supercomputing

To meet the demands of complex engineering and scientific calculations, one study by Yaroslav Nykolaychuk focuses on the development of high-performance arithmetic logic coprocessors for supercomputers. These coprocessors achieve high computation speed and efficiency by optimizing basic operations such as addition, accumulation, and multiplication, while also reducing hardware complexity. In these designs, ALUs serve as a critical component, executing arithmetic and logic operations with extremely high throughput, which is crucial for maintaining the overall performance of the coprocessor. By employing advanced encoding methods, these coprocessor structures further improve computational reliability and speed when processing multi-bit data. This makes supercomputers significantly more efficient for complex engineering, scientific research, and resource-intensive tasks, demonstrating great potential in multi-core and supercomputing environments [7].

3.4. Optimization Using Gate Diffusion Input (GDI) Technology

In modern embedded systems, reducing circuit area while minimizing power consumption is a key challenge in ALU design. One study by Vivechana Dubey has employed Gate Diffusion Input (GDI) technology to design a low-power 4-bit ALU. GDI technology reduces the number of transistors and decreases the load on signal transmission paths, thereby significantly reducing circuit area and energy consumption. Compared to traditional CMOS designs, GDI technology has demonstrated substantial advantages in terms of power consumption and circuit delay, making it an ideal choice for embedded applications that require both high performance and low power consumption [8].

3.5. Application of Dual Mode Logic (DML) in ALU

To balance power consumption and speed in different application scenarios, one study by Neetika Yadav has proposed using Dual Mode Logic (DML) technology to optimize ALU design. DML technology combines the benefits of static CMOS and dynamic CMOS, allowing for effective power reduction in static mode and enhanced computation speed in dynamic mode. This design allows the ALU to flexibly switch between low power and high performance based on system load conditions, enabling better performance in multitasking environments. It is particularly suitable for computing applications with stringent requirements on both power consumption and performance [9].

3.6. Optimization Using Single Electron Transistor (SET) Technology

As device sizes continue to shrink, Single Electron Transistor (SET) technology has emerged as a potential alternative to traditional CMOS due to its low power consumption and high sensitivity. One study by Rathin Joshi has shown that the 4-bit ALU designed using SET technology demonstrates superior performance in terms of power consumption, delay, and power-delay product (PDP) compared to traditional CMOS circuits. Specific optimizations include refining the SET units at deep submicron levels to ensure stable operation at room temperature. Studies have shown that SET technology enhances the energy efficiency of ALUs, making it particularly relevant for future nanoscale, low-power devices [10].

3.7. Optimization by Combining Quantum Cellular Automata (QCA) and Reversible Logic

To address the power consumption and heat dissipation challenges of traditional logic circuits, one study by A. Kamaraj has proposed combining Quantum Cellular Automata (QCA) with reversible logic gates in ALU design. The properties of QCA make it well-suited for implementing efficient computations at the nanoscale, while reversible logic gates reduce power dissipation by minimizing information loss. The integration of QCA and reversible logic gates in ALU design effectively controls quantum cost and garbage outputs, thus reducing overall power consumption. This approach not only improves the energy efficiency of ALUs but also provides a highly efficient solution for fields like quantum computing and optical computing [11].

4. Conclusion

In this paper, various application scenarios and optimization strategies for Arithmetic Logic Units (ALUs) has been examined. Focusing on their applications in embedded systems, quantum computing, and high-performance computing. Techniques such as approximate arithmetic units, reversible logic, Gate Diffusion Input (GDI) technology, and Single Electron Transistor (SET) technology have demonstrated potential for improving computational efficiency, reducing power consumption, and enhancing processing speed. These methods address different needs, ranging from low-power solutions for embedded systems to high-speed designs suitable for superconducting environments.

Despite the advancements, several challenges persist in optimizing ALU designs. Balancing power efficiency with computational accuracy remains a significant issue, particularly in scenarios where even minimal inaccuracies can impact outcomes. The integration of emerging technologies like Quantum Cellular Automata (QCA) and SETs into conventional computing architectures also presents technical hurdles, including compatibility and scalability. Furthermore, adapting ALU designs for new computing paradigms like quantum and neuromorphic computing requires innovative approaches.

Looking ahead, future research should aim to address these challenges by developing hybrid models that combine the strengths of multiple technologies. This could enable more adaptable and efficient ALUs capable of meeting the evolving demands of diverse computing environments. By focusing on both performance optimization and scalability, the next generation of ALUs can contribute significantly to advancements in computing technology.